# ITC 2023 PO 40: Efficiency of packetized data delivery in 2.5D/3D designs

Peter Orlando, Kacper Grubich, Mateusz Czartoryski

# SIEMENS

## Abstract

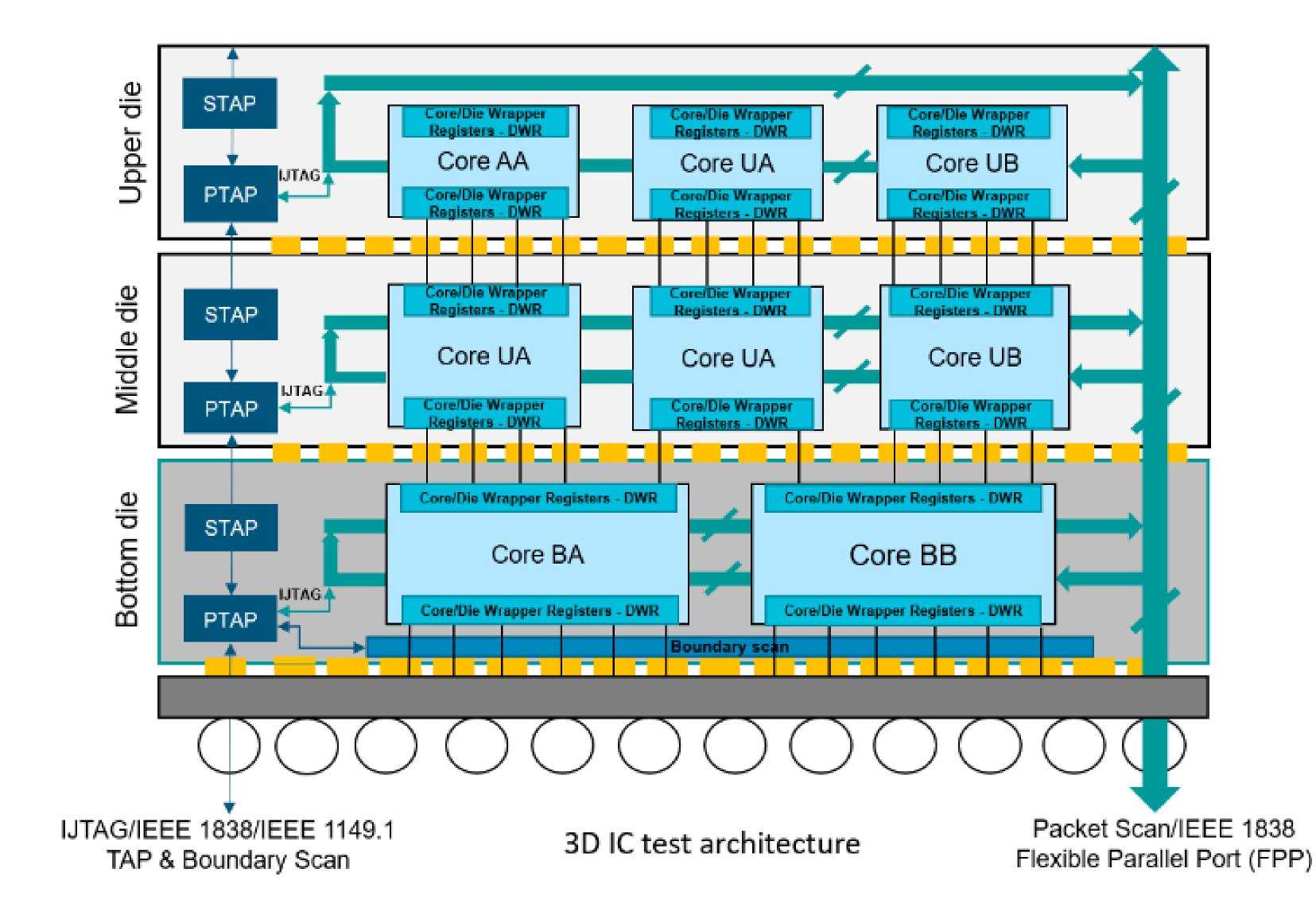

With the growing complexity of Integrated Circuits (ICs), packetized scan data has shown to be a major component in test time reduction. With a packetized scan interface scan data is distributed to all cores concurrently. The optimization can include independent compression for all cores, resulting in an improvement in test time and pattern count reduction. Designs with 2.5D/3D architecture also benefit from parallel bus techniques as it simplifies the deployment of Design For Test (DFT) significantly.

### Limitations without Flexible Parallel Port (FPP)

#### **Comparison between non-FPP and FPP design**

- 1. TAP access limits the scan bus to one bit

- 2. Low test clock (1149.1 TCK) frequency

- 3. High-effort routing and timing closure of test signals

- 4. No safety backup mechanism

| Description   | Without FPP                    | With FPP                   |  |

|---------------|--------------------------------|----------------------------|--|

| Scan          | Scan data shifted through TAP  | Scan data shifted through  |  |

| Delivery      | controllers and IJTAG network  | the bus (IJTAG access as a |  |

|               |                                | backup mechanism)          |  |

| Bus clocking  | 1149.1 test clock              | Independent bus clock      |  |

| Access to     | In-series Test Access Ports    | Mux-based parallel bus     |  |

| adjacent dies | (TAPs) configuration fo        |                            |  |

| (2.5D)        |                                | bypassing unused dies      |  |

|               |                                | (TAPs as a backup)         |  |

| Access to     | In-series Primary TAPs (PTAPs) | Direct access through the  |  |

| upper-level   | and Secondary TAPs (STAPs)     | dies - mux-based           |  |

| dies (3D)     |                                | configuration to access    |  |

|               |                                | the internal die logic     |  |

| Test signal   | Sourced from stack boundary    | Locally generated for      |  |

| management    | and routed to all dies         | each core inside each die  |  |

| Compression   | Pin-mux based configuration,   | Number of input/output     |  |

| logic         | dependent on the number of     | channels independent       |  |

|               | pins                           | from the number of pins,   |  |

# **Benefits of the parallel bus**

- Implementation of FPP that allows data packetizing for scan data delivery provides independent test signal sources for each die. This way cores within a die can be run concurrently while having a predictable, local timing to each core.

- Parallel access enables multiple-bit bus width. Combined with higher bus clock frequency the bus provides high throughput.

- Additional data delivery method makes the IJTAG access a backup mechanism in case the bus is inoperative

connected to FPP logic

CoreAll cores dependent onCores run concurrentlydependencyshared global test signalthanks tolocallyduring testssourcesgenerated test signals

# **Die-level considerations**

- With packetized data delivery the cores are encapsulated – changes in these cores are not visible from a die-level perspective

- Test signals don't span hierarchy boundaries. This simplifies routing at all levels

#### **Summary**

Packetized data delivery improves testability through parallel access. Utilizing locally generated signals allows easier timing analysis. Compliance with tile-based and multi-dimensional design makes it a dependable solution for these architectures.

# **Possible test time reduction**

| <b>Bus width</b> | TAP/IJTAG access            | FPP access |

|------------------|-----------------------------|------------|

| One bit          | 1x*                         | Nx**       |

| M bits           | 1x (wider bus is forbidden) | (NxM)x     |

\* Test clock without FPP acts as a reference clock

\*\* N is calculated as the frequency ratio of the FPP bus clock to the 1149.1 test clock

### References

[1] *"*IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits," in IEEE Std 1838-2019, vol., no., pp.1-73, 13 March 2020, doi: 10.1109/IEEESTD.2020.9036129.